Static void cs553x_data_in(struct cs553x_nand_controller *cs553x, void *buf, Ret = readb_poll_timeout_atomic(cs553x->mmio + MM_NAND_STS, status, #define FLSH_LBAR_EN (1ULLmmio + MM_NAND_CTL) #define MSR_DIVIL_LBAR_FLSH3Đx51400013 /* Flash Chip Select 3 */ #define MSR_DIVIL_LBAR_FLSH2Đx51400012 /* Flash Chip Select 2 */ #define MSR_DIVIL_LBAR_FLSH1Đx51400011 /* Flash Chip Select 1 */ #define MSR_DIVIL_LBAR_FLSH0Đx51400010 /* Flash Chip Select 0 */ #define MSR_NANDF_RSVD 0x5140001d /* Reserved */ #define MSR_NANDF_CTL 0x5140001c /* NAND Flash Control Timing */

#define MSR_NANDF_DATA 0x5140001b /* NAND Flash Data Timing MSR */ #define MSR_DIVIL_GLD_CAPĐx51400000 /* DIVIL capabilitiies */ * where 0-3 reflects the chip select for NAND.

* mtd-id for command line partitioning is cs553x_nand_cs * the AMD CS5535/CS5536 companion chipsets for the Geode processor. This video shows the XOR gate and then the XNOR gate on the home made CPLD board.* This is a device driver for the NAND flash controller found on The JED file is for configuring the home made CPLD board. The VHDL code listing below shows the same code as above, but with compensation for inverting inputs and outputs on the board.ĭownload xor_xnor.zip (5.9kB) which contains the VHD, UCF and JED files for the XOR and XNOR gates. Y1 <= B1 xnor B2 - 2 input exclusive-NOR gate X1 <= A1 xor A2 - 2 input exclusive-OR gate Port ( A1 : in STD_LOGIC - XOR gate input 1Īrchitecture Behavioral of xor_xnor_top is

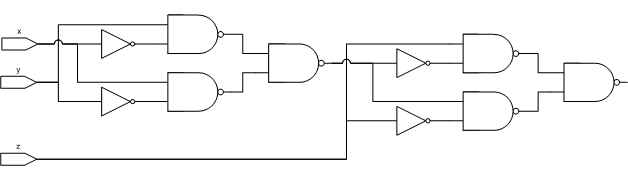

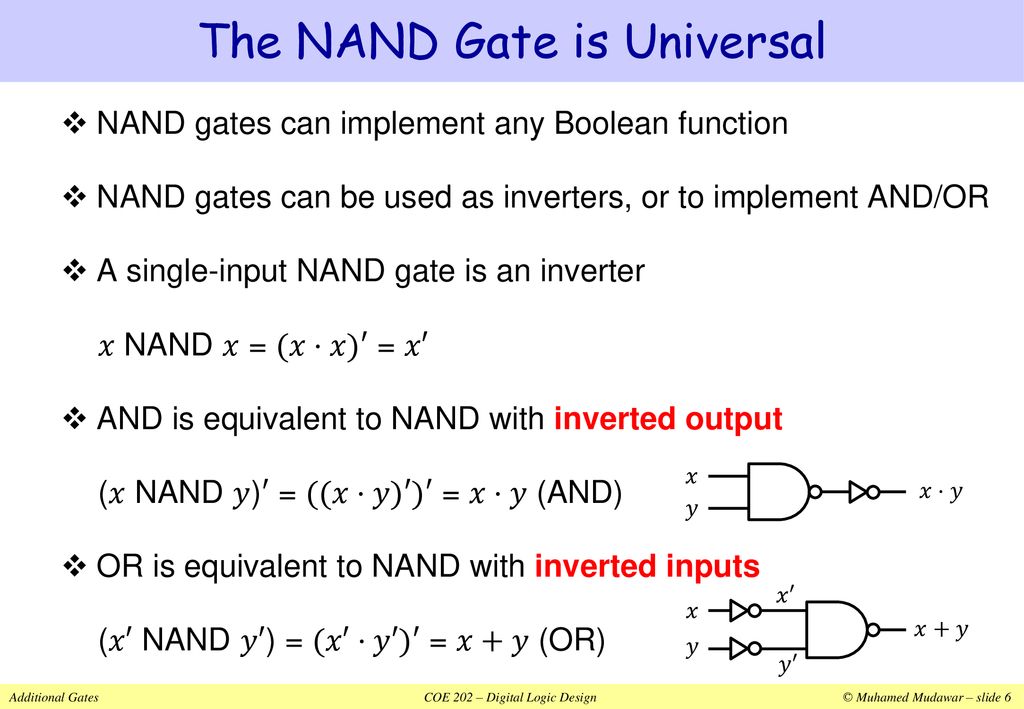

This listing shows an XOR and XNOR gate in VHDL. The VHDL xnor keyword is used to create an XNOR gate: XNOR Gate with Truth Table and VHDL XOR and XNOR VHDL Project The VHDL xor keyword is used to create an XOR gate: XOR Gate with Truth Table and VHDL XNOR Gate This video shows the NAND gate and then the NOR gate implemented on the home made CPLD board.īooks that may interest you: Exclusive-OR and Exclusive-NOR Logic Gates in VHDL XOR Gate compensation for inverting inputs and outputsĭownload nand_nor.zip (5.9kB) which contains the VHD, UCF and JED files for the NAND and NOR gates. The need for compensation is explained in tutorial 2 AND Gates, OR Gates and Signals in VHDL. The code listing below shows the same code as above, but with compensation for the inverting inputs on the home made Xilinx CPLD board. Port ( A1 : in STD_LOGIC - NAND gate input 1Īrchitecture Behavioral of nand_nor_top is Two separate gates are created that each have two inputs. This code listing shows the NAND and NOR gates implemented in the same VHDL code. The VHDL nor keyword is used to create a NOR gate: NOR Gate with Truth Table and VHDL NAND and NOR VHDL Project The VHDL nand keyword is used to create a NAND gate: NAND Gate with Truth Table and VHDL NOR Gate NAND and NOR Logic Gates in VHDL NAND Gate

0 kommentar(er)

0 kommentar(er)